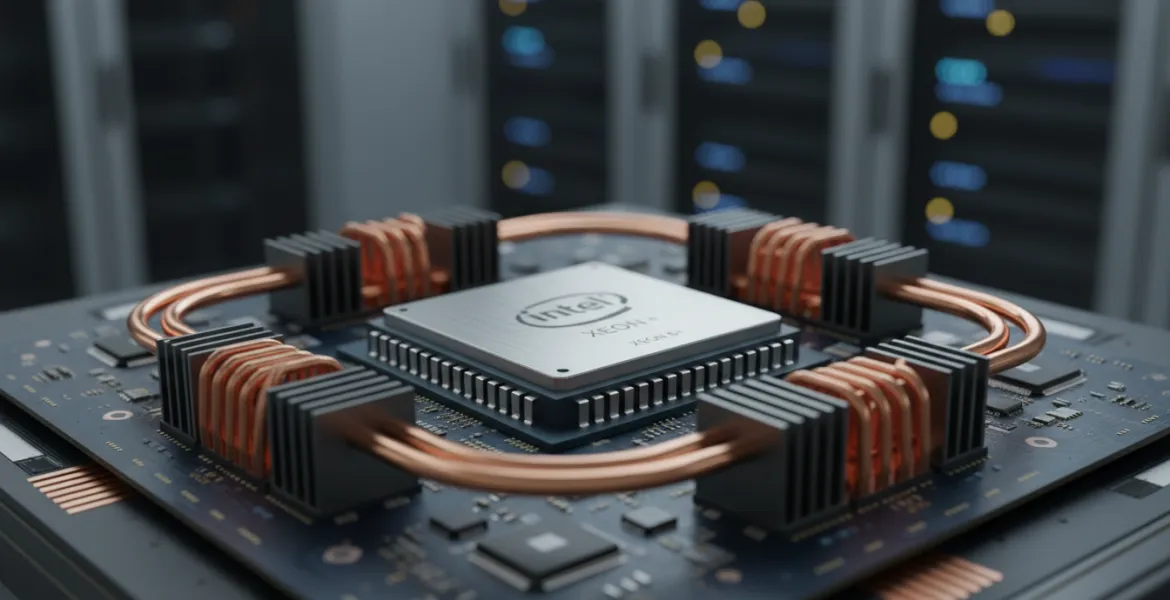

Intel ha colto l'occasione del MWC 2026 per offrire un'anteprima dei suoi prossimi processori server Intel Xeon 6+ (nome in codice Clearwater Forest). L'azienda li descrive come il passo successivo nella roadmap Xeon 6, pensati per l'infrastruttura di rete e cloud con un focus sull'accelerazione dell'intelligenza artificiale (IA). Durante l'evento, Intel ha anche mostrato fisicamente i processori.

Secondo le slide presentate da Intel, gli Xeon 6+ sfruttano 12 blocchi di calcolo basati sul processo produttivo Intel 18A, che include i transistor RibbonFET (con gate avvolgente) e il sistema di alimentazione PowerVia (sul retro del chip). La composizione include anche tre blocchi base attivi realizzati con tecnologia Intel 3 e due blocchi I/O (Input/Output Die) basati sul processo Intel 7. L'interconnessione tra i blocchi avviene tramite ponti EMIB (2.5D) e la tecnologia di packaging Foveros Direct 3D.

Un'analisi più dettagliata delle slide di Intel rivela che ciascun blocco di calcolo è composto da 6 moduli, ognuno contenente 4 core. Questo si traduce in 24 core Darkmont E per blocco. Intel dichiara che i processori Xeon 6+ possono arrivare fino a 288 core Darkmont E, grazie all'integrazione di 12 blocchi di calcolo, ognuno con 24 E-core. I chip supporteranno configurazioni sia a singolo che a doppio socket.

Ogni modulo dispone di 4 MB di cache L2 condivisa. Il blocco I/O include otto acceleratori, tra cui le tecnologie Intel QuickAssist, Intel Dynamic Load Balancer, Intel Data Streaming Accelerator e Intel In-Memory Analytics Accelerator. Ogni blocco I/O supporta 48 linee PCIe Gen 5.0, 32 linee CXL 2.0 e 96 linee UPI 2.0. Le slide indicano anche il riutilizzo dei die I/O dalla serie di processori Granite Rapids, suggerendo una strategia di ottimizzazione dei costi e dei tempi di sviluppo.

Per quanto riguarda la cache e il sottosistema di memoria, il blocco base include 192 MB di cache LLC (Last Level Cache) per blocco e 48 MB di cache LLC per blocco di calcolo, con supporto per quattro canali di memoria DDR5 per blocco base. In sintesi, la piattaforma supporterà configurazioni a 12 canali DDR5-8000, fino a 576 MB di LLC, 96 linee PCIe Gen 5 e 64 linee CXL, in configurazioni a singolo e doppio socket. Il TDP (Thermal Design Power) degli Xeon 6 dovrebbe variare tra 300 W e 500 W.

Secondo le previsioni di Intel, il lancio della serie di processori server Xeon 6+ è previsto per la prima metà del 2026. Questi processori rappresentano un passo significativo verso l'evoluzione delle infrastrutture server, con un'architettura ottimizzata per i carichi di lavoro emergenti nel campo dell'intelligenza artificiale e del cloud computing. L'integrazione di tecnologie avanzate come RibbonFET, PowerVia e l'interconnessione tramite EMIB e Foveros Direct, promette un aumento significativo delle prestazioni e dell'efficienza energetica, rispondendo alle crescenti esigenze dei data center moderni.